enggan

Member level 1

Hi Friends

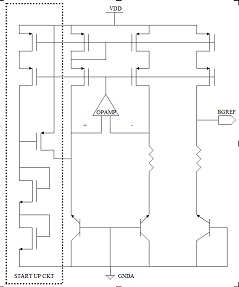

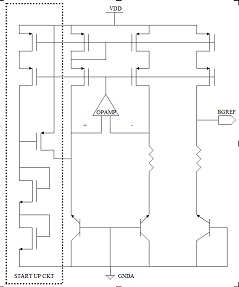

I am designing a bandgap reference circuit in .18um process shown in figgure. my objective is to get a stable output voltage with least temco as possible when i simulated my bandgap i got 1.125v as the voltage which has least temp co but usually 1.25v is the desired bandgap voltage if i set my output voltage to 1.25v my temp co worsens Please help why is this happening.

further i am using the following circuit diagram please suggest the limitations and benifits of this architecture. any suggestions to improve it

Thanks and regards

I am designing a bandgap reference circuit in .18um process shown in figgure. my objective is to get a stable output voltage with least temco as possible when i simulated my bandgap i got 1.125v as the voltage which has least temp co but usually 1.25v is the desired bandgap voltage if i set my output voltage to 1.25v my temp co worsens Please help why is this happening.

further i am using the following circuit diagram please suggest the limitations and benifits of this architecture. any suggestions to improve it

Thanks and regards