mycw

Junior Member level 3

Hello everyone,

I have encountered a problem with thin film resistor simulation, and I hope someone could give me a hand on this. Thanks in advance!

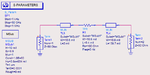

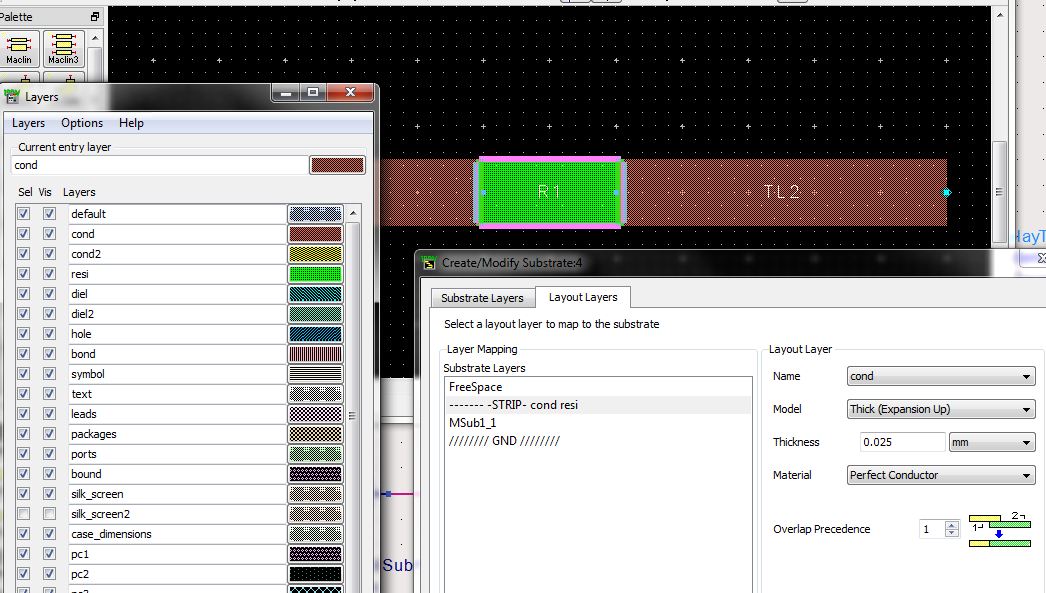

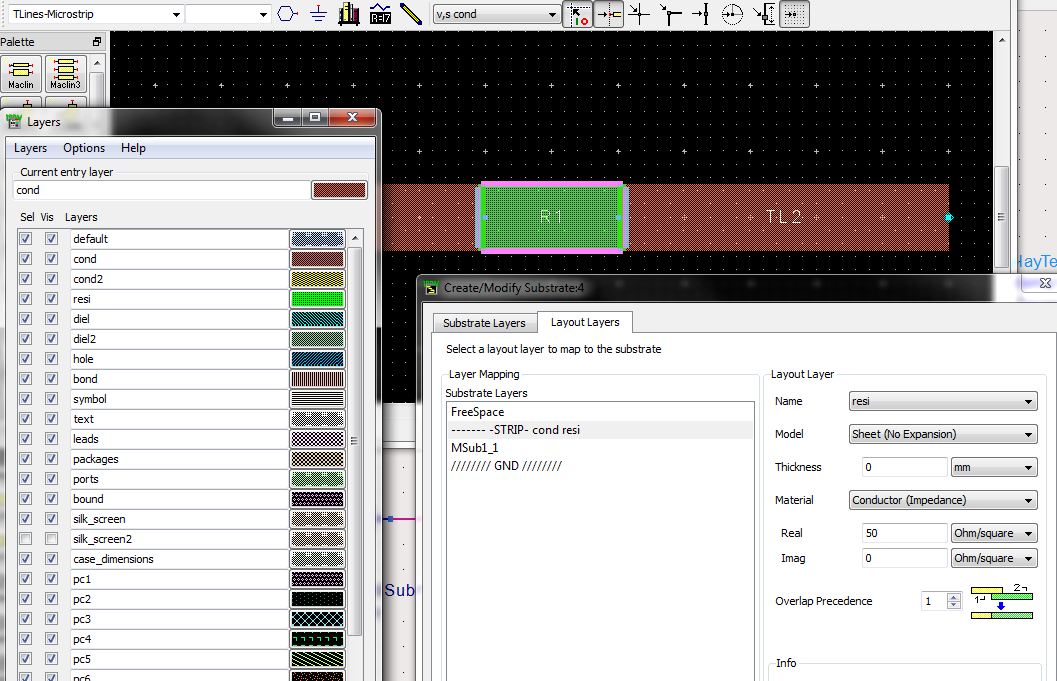

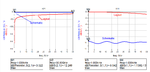

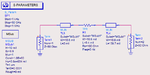

It's a simple design with TFR and microstrip, but simulation results from schematic and layout are quite different, I checked several time but I couldn't find any inconsistency in the settings, so I'm wondering if that is "normal"?

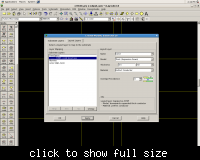

Schematic, layout with substrate settings, and s-parameter results of both simulation are attached. BTW, I checked with someone working on the fabrication, and I was told that the resistance layer has little impact on the simulation (Titanium, 20nm of thickness, and 100-Ohm/sq), thus it can be ignored, is it correct? But no matter how, the "substrate" of TFR in both designs are identical, thus this result was totally unexpected. Any clue?

Thank you,

Mario Young

I have encountered a problem with thin film resistor simulation, and I hope someone could give me a hand on this. Thanks in advance!

It's a simple design with TFR and microstrip, but simulation results from schematic and layout are quite different, I checked several time but I couldn't find any inconsistency in the settings, so I'm wondering if that is "normal"?

Schematic, layout with substrate settings, and s-parameter results of both simulation are attached. BTW, I checked with someone working on the fabrication, and I was told that the resistance layer has little impact on the simulation (Titanium, 20nm of thickness, and 100-Ohm/sq), thus it can be ignored, is it correct? But no matter how, the "substrate" of TFR in both designs are identical, thus this result was totally unexpected. Any clue?

Thank you,

Mario Young