yeknight

Newbie level 4

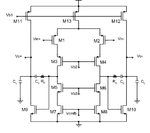

I am designing a fully differential telescope OPAMP,but can not let all the mosfets work in Saturati,How do I set a good static work point to a fully differential telescope OPAMP?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

I guess your netlist Vdc sources don't match your schematic:Vdd vdd 0 3.5V

Vss vss 0 0V

VB1 vb1 0 0.89V

VB2 vb2 0 1.57V

VB3 vb3 0 0.97V

VB4 13 0 2.27V

schematic <--> netlist

Vb1 VB4

Vcmbf VB1

vgs 3.0414

vds 53.4708m

vbs 0.

vth 661.4235m

vdsat 1.5057