chanducs24

Member level 2

hi,

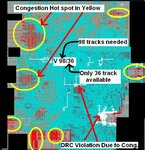

is there any other solution rather than density screens to reduce congestion.

Thanks,

chandra.

is there any other solution rather than density screens to reduce congestion.

Thanks,

chandra.