allennlowaton

Full Member level 5

Hello everybody,

Please help me with this.

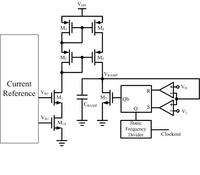

I'm doing a clock generator from a ramp and the figure is shown below.

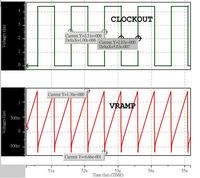

My concern is although using the circuit I was able to obtain a 1MHz from a VDD=2.7~5.5V,

the resulting ramp is not within the VH and VL limit. Am I doing the right track?

Shown below are the resulting simulations..

.

.

Thank you for taking time reading this one.

---------- Post added at 08:57 ---------- Previous post was at 08:56 ----------

I'm using VH = 1.2V and VL = 0.6V

Please help me with this.

I'm doing a clock generator from a ramp and the figure is shown below.

My concern is although using the circuit I was able to obtain a 1MHz from a VDD=2.7~5.5V,

the resulting ramp is not within the VH and VL limit. Am I doing the right track?

Shown below are the resulting simulations..

.

.Thank you for taking time reading this one.

---------- Post added at 08:57 ---------- Previous post was at 08:56 ----------

I'm using VH = 1.2V and VL = 0.6V