steadymind

Full Member level 4

hi all,

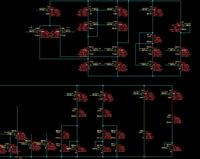

I am designing a bandgap with Cabrini, 2005 paper as a reference . i have attached the schematic from the paper. due to my process constraints , i am using pmos input folded cascode , and i find that i dont get classic curve. i get a linearly varing output.

i have a feeling that the way i generate the bias voltage for pmos current sources are the problem ?

Has anyone come across this type of problem... also from the paper it is unclear how they generate the bias voltage for the current mirrors.

ADDED : dc bias condition of schematic

I am designing a bandgap with Cabrini, 2005 paper as a reference . i have attached the schematic from the paper. due to my process constraints , i am using pmos input folded cascode , and i find that i dont get classic curve. i get a linearly varing output.

i have a feeling that the way i generate the bias voltage for pmos current sources are the problem ?

Has anyone come across this type of problem... also from the paper it is unclear how they generate the bias voltage for the current mirrors.

ADDED : dc bias condition of schematic

Attachments

Last edited: