jp619

Junior Member level 1

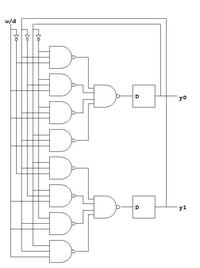

sequential circuits are the ones which depend on present and pass input values.... then if an AND gate is given a feedback from its output, does it become a sequential circuit??? justify..