vfurlan

Full Member level 2

I designed a active filter for PLL but the loop is out of lock.

Parameters of my PLL-VCO are

VCO gain Kvco = 60 - 80MHz/V

Phase detector gain Kv = 0.32 rad/V

loop bandwidth Fc = 10 000Hz

N = 22

φ = 45

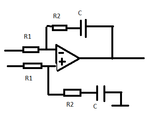

I'm using AD 8622 OP-AMP.

R1 = 312kΩ (used 330k)

R2 = 15.9k (used 15k)

C = 1nF

I use a 250MHz signal and N = 22, so VCO oscillates at 5.5GHz.

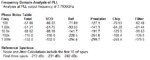

On schematic.png is a filter design, on filter.jpg you can see my filter, and on 5903.jpg the VCO respons.

Can you advise me what to do?

Thank you

Parameters of my PLL-VCO are

VCO gain Kvco = 60 - 80MHz/V

Phase detector gain Kv = 0.32 rad/V

loop bandwidth Fc = 10 000Hz

N = 22

φ = 45

I'm using AD 8622 OP-AMP.

R1 = 312kΩ (used 330k)

R2 = 15.9k (used 15k)

C = 1nF

I use a 250MHz signal and N = 22, so VCO oscillates at 5.5GHz.

On schematic.png is a filter design, on filter.jpg you can see my filter, and on 5903.jpg the VCO respons.

Can you advise me what to do?

Thank you