howardtang85

Newbie level 6

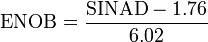

Does anyone know how to simulate the ENOB of a Charge Redistribution SAR ADC based on cadence spectre simulator?

Thanks!

Thanks!

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.