pz5921087

Member level 1

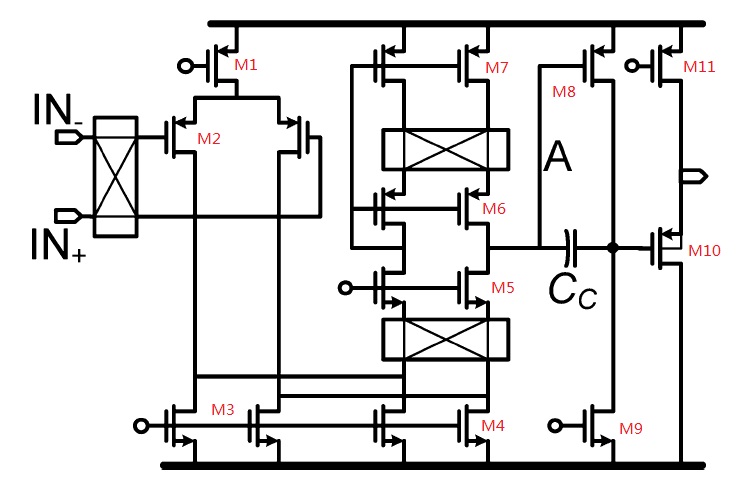

The picture shows the circuit.

Now I have a problem is that the phase margin is not enough, around 45 degree, the dc gain is 110dB, I think decrease the gain can increase the phase margin as well as the bandwidth. But I don't know how to keep the GBW unchanged and decrease the gain, increase the bandwidth at the same time. I try to increase the cap value for compensation before to increase the phase margin, but it does not work, if the cap value increases a lot, the bandwidth will sharply decrease. Please help me to solve this problem. Thanks!