hktk

Junior Member level 3

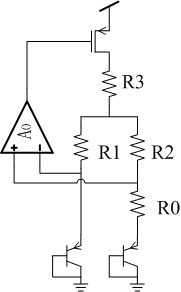

the simulation results of BG is around 1.22 but the tapeout results is 1.3~1.4. The structure is common, but L=2u for current mirror and W=2u L=30u for Res. Can any body give me some suggestion for the huge deviation between simulation and tapeout?

---------- Post added at 14:07 ---------- Previous post was at 14:05 ----------

R3 will save area of chip, but at same time R3 will amplify Vos of Opamp to reference voltage.

---------- Post added at 14:07 ---------- Previous post was at 14:05 ----------

R3 will save area of chip, but at same time R3 will amplify Vos of Opamp to reference voltage.