allennlowaton

Full Member level 5

Good day EDA fellows...

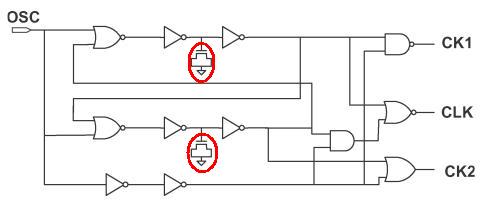

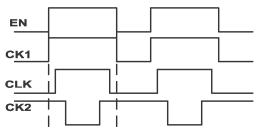

I'm having this 3 output non-overlapping clock generator circuit.

I'm having concern regarding those 2 MOS (drain and source connected). What's their purpose?

Thank you very much for spending time on this thread.

I'm having this 3 output non-overlapping clock generator circuit.

I'm having concern regarding those 2 MOS (drain and source connected). What's their purpose?

Thank you very much for spending time on this thread.