andrea22

Junior Member level 2

Does anyone know how it works non-overlapping clock generator?

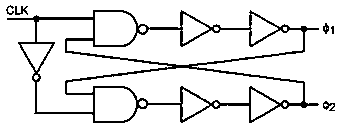

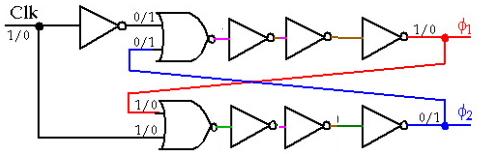

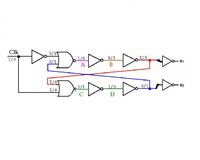

The circuit takes a clock signal and generates a two-phase nonoverlapping clock.

The amount of the separation is set by the delay trough the NAND gate and two inverters on the NAND output.

My question is:Why these clock signal must me non-overlapped?

How each logic gate (NAND and inverters) effects that those signals are non-overlapped?

How can non-overlapping time increase?

The circuit takes a clock signal and generates a two-phase nonoverlapping clock.

The amount of the separation is set by the delay trough the NAND gate and two inverters on the NAND output.

My question is:Why these clock signal must me non-overlapped?

How each logic gate (NAND and inverters) effects that those signals are non-overlapped?

How can non-overlapping time increase?