allennlowaton

Full Member level 5

good day EDA fellows...

I got this PWM controller IC from a paper. From a figure below, there's a

one shot module after the oscillator. By the way, this oscillator utilizes a frequency spread technique. The oscillator produces a variable period with a fixed 50% duty cycle.

The paper said that the purpose of the one shot module is to rectify the duty cycle to a small value in order to avoid unexpected logic locking. I don't understand this statement. Please shed some light on this.

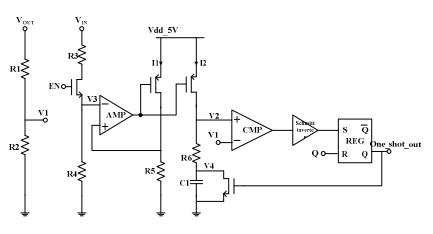

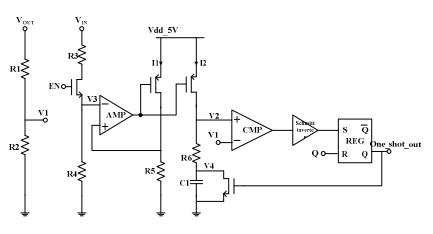

Below is the diagram of a one shot, I got from the other paper but the same author:

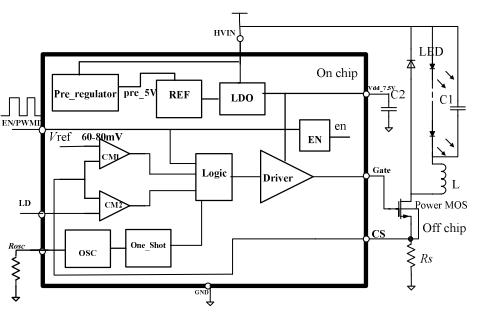

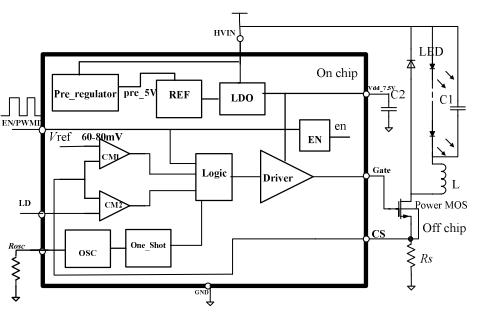

Below is the diagram of the PWM controller IC:

I got this PWM controller IC from a paper. From a figure below, there's a

one shot module after the oscillator. By the way, this oscillator utilizes a frequency spread technique. The oscillator produces a variable period with a fixed 50% duty cycle.

The paper said that the purpose of the one shot module is to rectify the duty cycle to a small value in order to avoid unexpected logic locking. I don't understand this statement. Please shed some light on this.

Below is the diagram of a one shot, I got from the other paper but the same author:

Below is the diagram of the PWM controller IC: