yixiusky

Member level 2

Hello everyone

I would like to ask one question

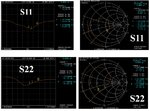

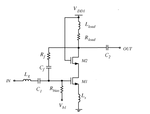

I designed one LNA works frome 1.8 to 2.2 GHz. After meausrement, the input and output matching are ok, but the gain shiift to 1.5GHz. I could not think the reason. Could you help me?

Thank you very much.

I would like to ask one question

I designed one LNA works frome 1.8 to 2.2 GHz. After meausrement, the input and output matching are ok, but the gain shiift to 1.5GHz. I could not think the reason. Could you help me?

Thank you very much.