laserbeak43

Member level 1

- Joined

- Aug 15, 2008

- Messages

- 33

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,288

- Location

- Maryland, USA

- Activity points

- 1,491

Hello,

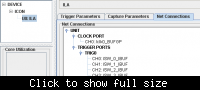

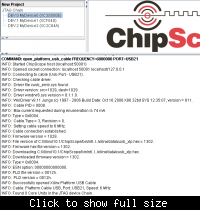

I'm using Chipscope and the ISE 10.1 suite and i can't get it to work.

and this doesn't even work. I've read xilinx's chipscope doc and decyphered what i could, but it still left me googling for tutos and i still get the same results after reading this one **broken link removed**

can someone please help?

I'm using Chipscope and the ISE 10.1 suite and i can't get it to work.

I'm using some very simple codeERROR:ChipScope: One or more invalid signal connections detected.

ERROR:ChipScope: Double-click the scope.cdc icon in the sources window to edit and fix the CDC project.

ERROR: Chipscope Insertion failed

Code:

module two_input_xor (

input wire in1,

input wire in2,

output wire out

);

assign out = in1 ^ in2;

endmodulecan someone please help?