gaom9

Full Member level 4

sigma delta verilog

Hi,

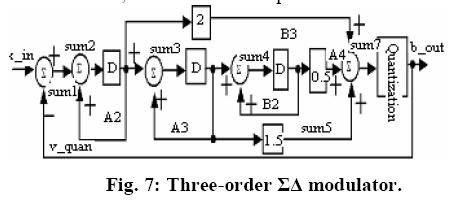

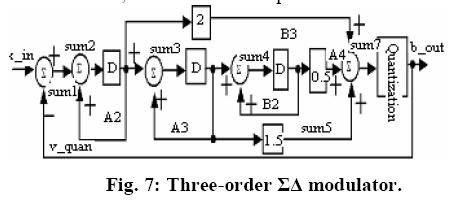

I am design a ΣΔ fractional- frequency synthesizer, and I find a verilog code for the digitao sigma-delta modulator, which is a single-loop multi-bits quantizer. The output is 5bit and the input is 22Bits. Its structure and the verilog code are shown below. But when I simulate this verilog code, the result is not right.

The input word-width is 22Bits, and I want to get a fraction of 0.25, so I add an input of 0.25×2(22)=1048576. But when I calculate the average of the output to the total nunber of clock, it equal to 1.8.

Is there any matter with the code? And is there any different between the input of MASH and single-loop, in MASH, the input = fraction × the word-width.

Please give some advice.

Thank you!

Best regards!

structure

Verilog-code and testbench

Hi,

I am design a ΣΔ fractional- frequency synthesizer, and I find a verilog code for the digitao sigma-delta modulator, which is a single-loop multi-bits quantizer. The output is 5bit and the input is 22Bits. Its structure and the verilog code are shown below. But when I simulate this verilog code, the result is not right.

The input word-width is 22Bits, and I want to get a fraction of 0.25, so I add an input of 0.25×2(22)=1048576. But when I calculate the average of the output to the total nunber of clock, it equal to 1.8.

Is there any matter with the code? And is there any different between the input of MASH and single-loop, in MASH, the input = fraction × the word-width.

Please give some advice.

Thank you!

Best regards!

structure

Verilog-code and testbench