calculus_cuthbert

Member level 4

Hi

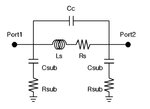

I have designed a CMOS LC VCO.

I want to improve the output swing of the VCO.

Pre layout simulations show that the output swing is 1.4 V (0.18u process)

But after laying out all the blocks the output swing drops to 0.8V peak to peak.

I would appreciate it if someone could help me figure out how to increase the output swing. Is it because of parasitic resistance that the gain is lowered?

The ground plane in my design is in the lower most metal.. should i change it to a metal layer with lower resistivity?

I have designed a CMOS LC VCO.

I want to improve the output swing of the VCO.

Pre layout simulations show that the output swing is 1.4 V (0.18u process)

But after laying out all the blocks the output swing drops to 0.8V peak to peak.

I would appreciate it if someone could help me figure out how to increase the output swing. Is it because of parasitic resistance that the gain is lowered?

The ground plane in my design is in the lower most metal.. should i change it to a metal layer with lower resistivity?