prcken

Advanced Member level 1

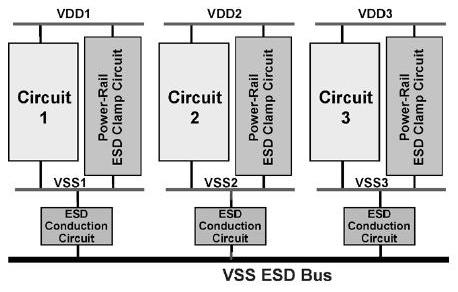

will you connect GND PAD through a dual diode to VSS rail or just connect to VSS rail directlly?

what's the pros and cons of both methods?

thanks!!!

:?:

:?:

what's the pros and cons of both methods?

thanks!!!