kaka.alonso

Newbie level 5

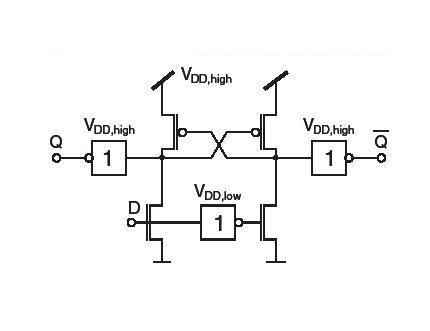

what is the mechanism of asynchronous level-shifter?

it is said a contention exists between the pull-down devices and the feed-back path

how to understand it?

thx

it is said a contention exists between the pull-down devices and the feed-back path

how to understand it?

thx