dinesh.4126

Member level 5

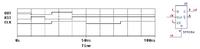

deassertion reset

Hi,

Interview Quest:In a sync. reset Design if duration of each clock width is of 50ns.and if reset is asserted at 10 ns and de-assert at 20ns and again assert at 40ns.then what is O/P.?

thanx,

Dinesh

Hi,

Interview Quest:In a sync. reset Design if duration of each clock width is of 50ns.and if reset is asserted at 10 ns and de-assert at 20ns and again assert at 40ns.then what is O/P.?

thanx,

Dinesh