electronXwork

Member level 3

- Joined

- Apr 27, 2007

- Messages

- 56

- Helped

- 4

- Reputation

- 8

- Reaction score

- 2

- Trophy points

- 1,288

- Activity points

- 1,623

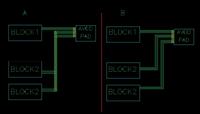

Power line layout

Hi all,

Please see the attached file for reference.

Initially I layout A for AVDD line but I was requested to do layout B. In A, notice the vertical line, to save space I overlaped M1 and M2 w/ via12 on them. In B, I was instructed to have a dedicated AVDD line for each block to the pad but by doing this I would not have enough space anymore for the other lines.

Please tell me why do they insisted B? I think A has the same current distribution as B. Does noise is related? Because I am thinking that it is possible that the line in block2 may accumulate noise and might be passed on to block3 or vice versa. Please clarify and if you have other reasons I will be thankful if you share them.

This is also applied to AVSS lines.

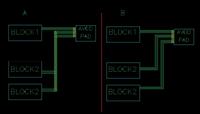

Hi all,

Please see the attached file for reference.

Initially I layout A for AVDD line but I was requested to do layout B. In A, notice the vertical line, to save space I overlaped M1 and M2 w/ via12 on them. In B, I was instructed to have a dedicated AVDD line for each block to the pad but by doing this I would not have enough space anymore for the other lines.

Please tell me why do they insisted B? I think A has the same current distribution as B. Does noise is related? Because I am thinking that it is possible that the line in block2 may accumulate noise and might be passed on to block3 or vice versa. Please clarify and if you have other reasons I will be thankful if you share them.

This is also applied to AVSS lines.