vlsitechnology

Full Member level 5

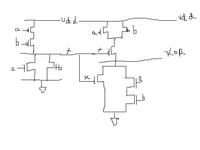

half adder schematic

Can anyone tell me the details of drawing the layout of half adder?

Added after 45 seconds:

I need to know the details without taking the spice levelnetlist

I mean with the help of boolean expression how can we draw the layout

Can anyone tell me the details of drawing the layout of half adder?

Added after 45 seconds:

I need to know the details without taking the spice levelnetlist

I mean with the help of boolean expression how can we draw the layout