GLR

Newbie level 4

- Joined

- Jul 10, 2024

- Messages

- 7

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 42

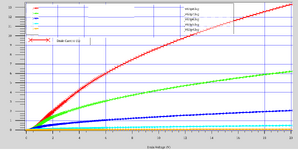

Hi guys... is it realistic the following simulates Rdson(iD) for a High Voltage SiC mosfet belonging to high-Ron class?

Is acceptable for you a similar Rdson(iD) of a commercial SiC mosfet?

What is your opinion?

[Ohm] vs [A]

Is acceptable for you a similar Rdson(iD) of a commercial SiC mosfet?

What is your opinion?

[Ohm] vs [A]

Last edited: