melkord

Full Member level 3

I usually use small signal formula to calculate output resistance (method 1).

But now want to find a simulation setup to measure it (method 2) so I do not need to input the expression of rout.

A good discussion I found from here and here.

I still do net get the same result between method 1 and method 2.

Could someone give me their correction to my setup?

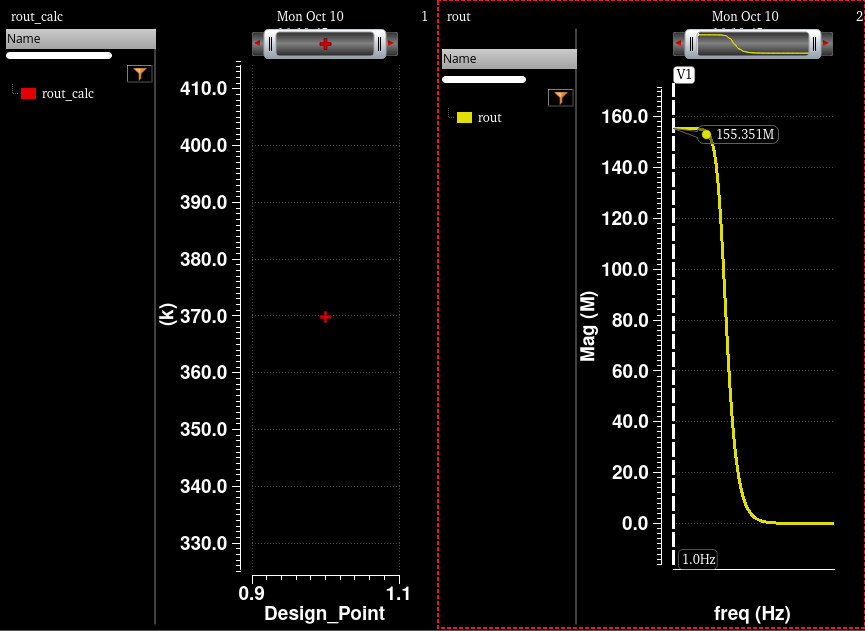

Result.

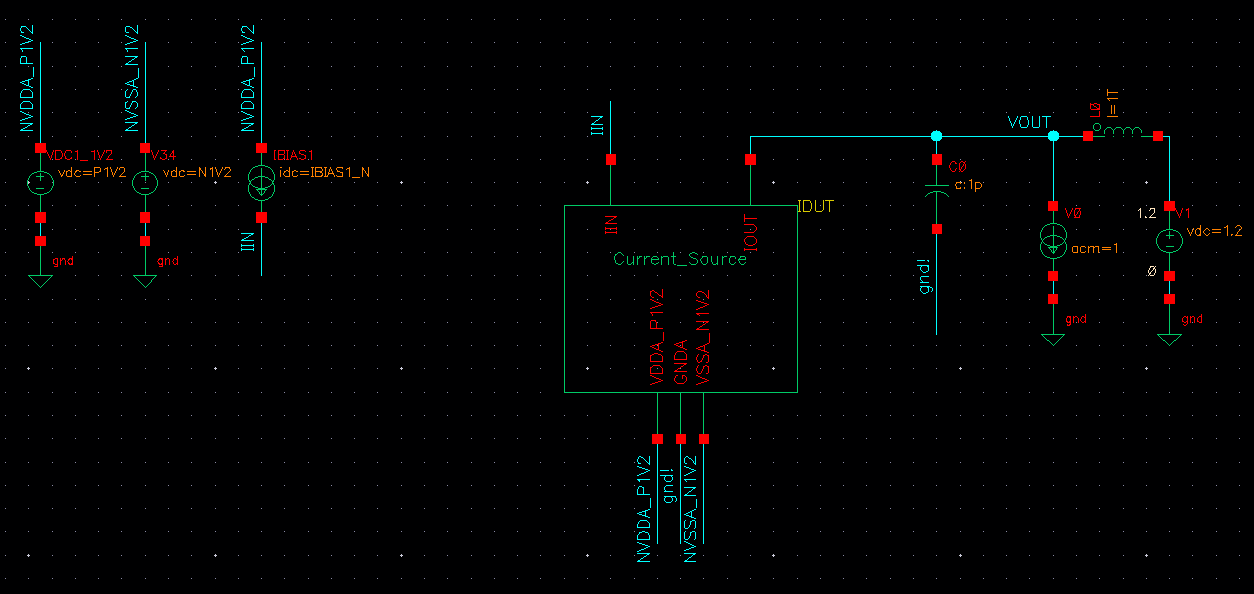

The testbench.

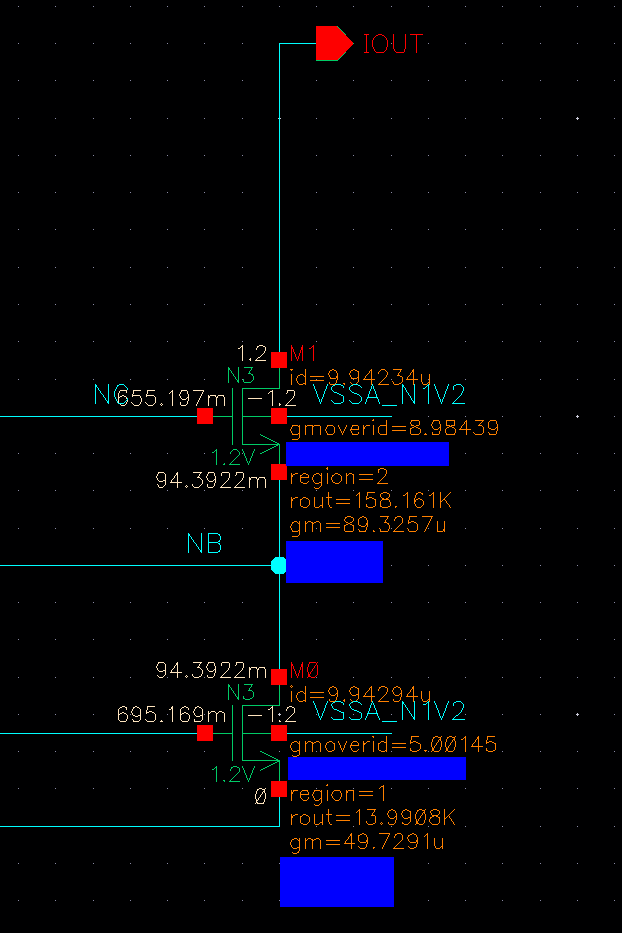

The output transistors.

But now want to find a simulation setup to measure it (method 2) so I do not need to input the expression of rout.

A good discussion I found from here and here.

I still do net get the same result between method 1 and method 2.

Could someone give me their correction to my setup?

Result.

The testbench.

The output transistors.