Adel Rein

Newbie

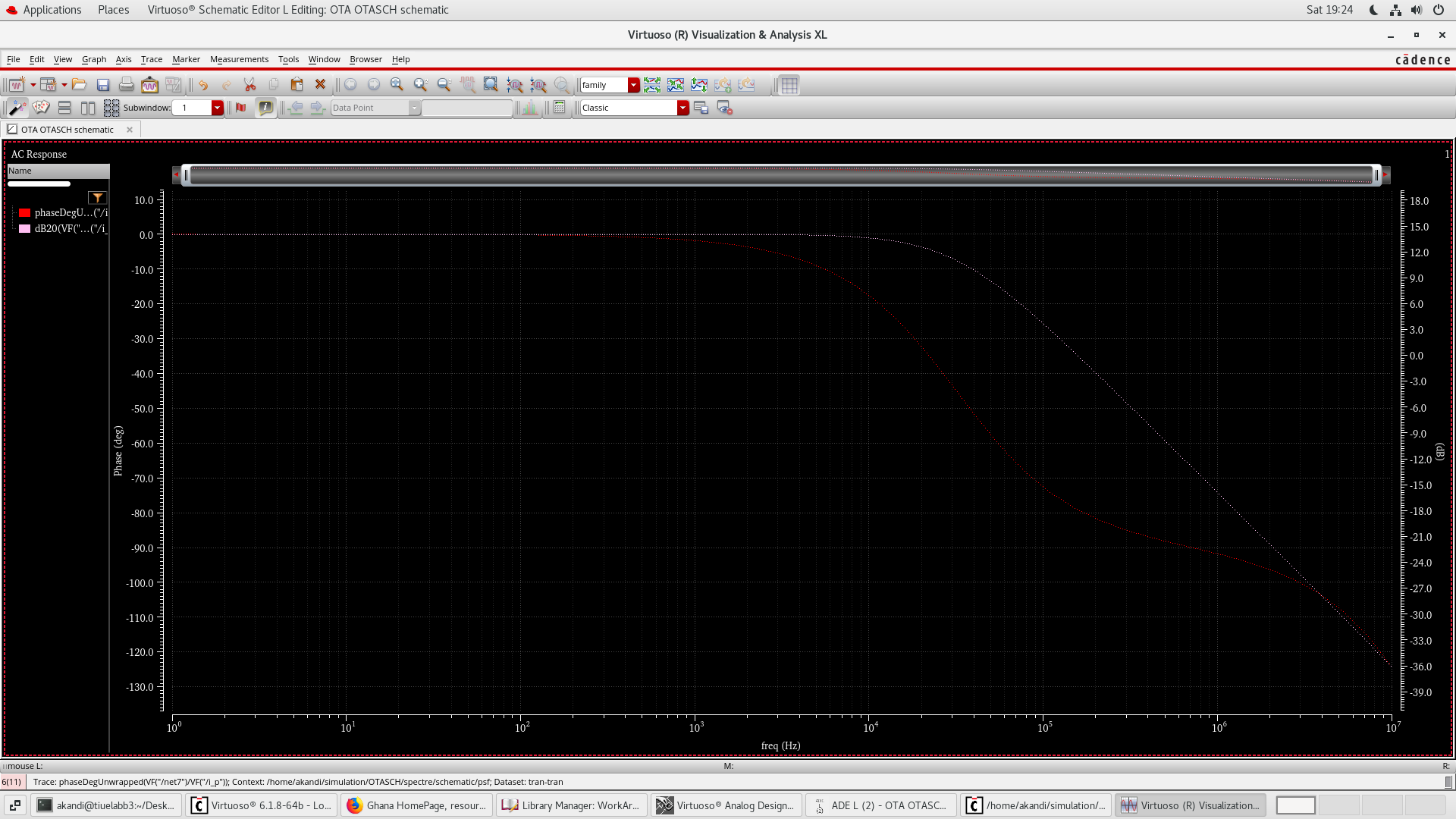

I did an ac analysis plot on a two stage OTA with the plot shown below

Is the graph correct, because I need to determine the gain bandwidth product and I am finding it difficult to find the gain bandwidth product. I am expecting a gain bandwidth product of 25M

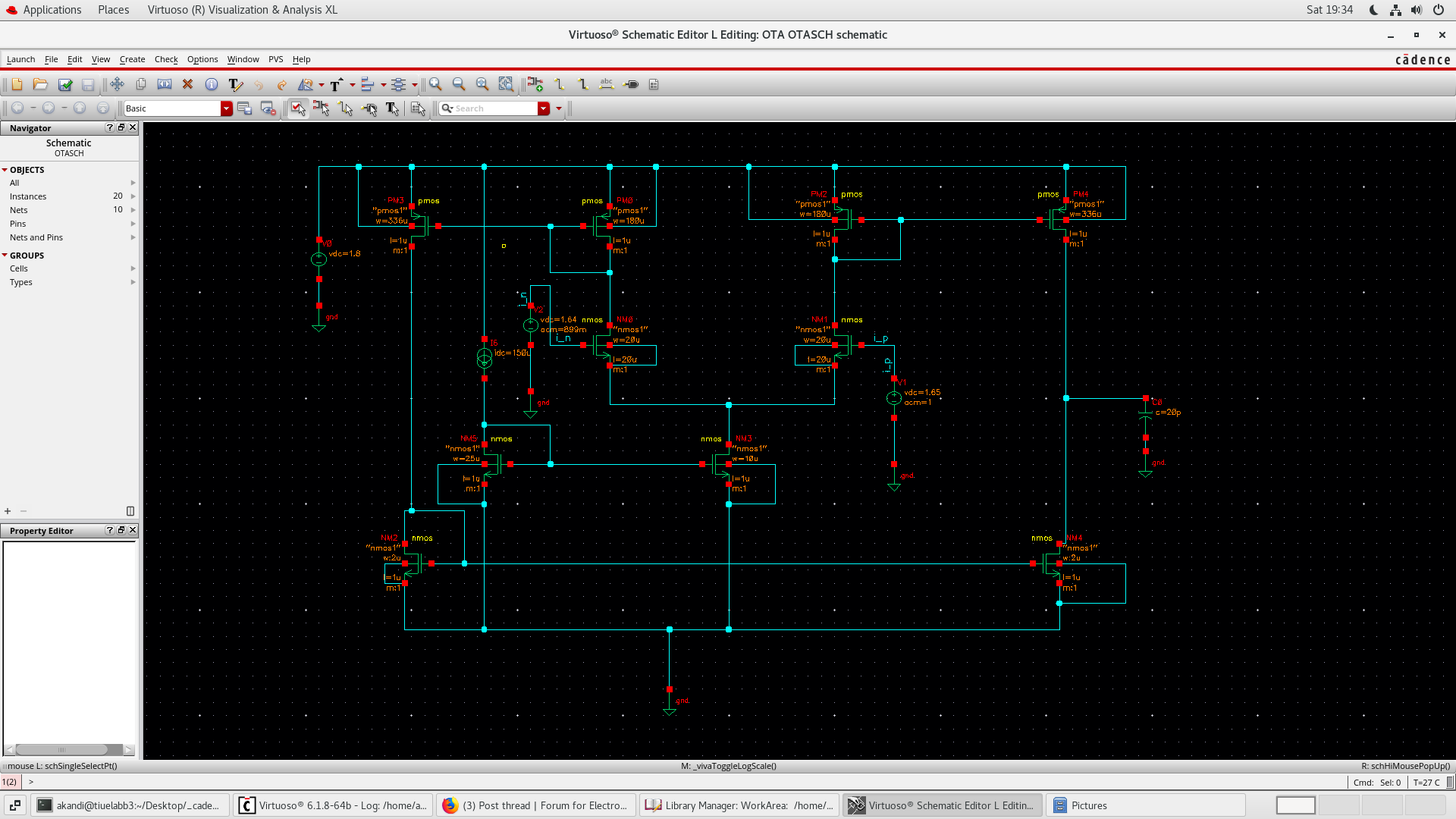

Below is the schematic

Is the graph correct, because I need to determine the gain bandwidth product and I am finding it difficult to find the gain bandwidth product. I am expecting a gain bandwidth product of 25M

Below is the schematic