FlyingDutch

Advanced Member level 1

- Joined

- Dec 16, 2017

- Messages

- 458

- Helped

- 45

- Reputation

- 92

- Reaction score

- 55

- Trophy points

- 28

- Location

- Bydgoszcz - Poland

- Activity points

- 5,027

Hello,

some time ago I described my struggling with implementatuion for very simple "SRAM controller" - see this link:

https://www.edaboard.com/threads/issue-with-port-buffering-inout-spartan7-board.395904/

After long time this struggle ended with success - this simple controller was working. The issue is that implementation had very bad performance and wasn't suitable for using in real project (for my needs only). It was the reason that I have started looking for better implementation of SRAM controller. I noticed that in "Xilinx Vivado" is available fre IPCore called "AXI EMC v.3.0" (this is shortcut for: AXI External Memory Controller) - see this link:

https://www.xilinx.com/support/documentation/ip_documentation/axi_emc/v3_0/pg100-axi-emc.pdf

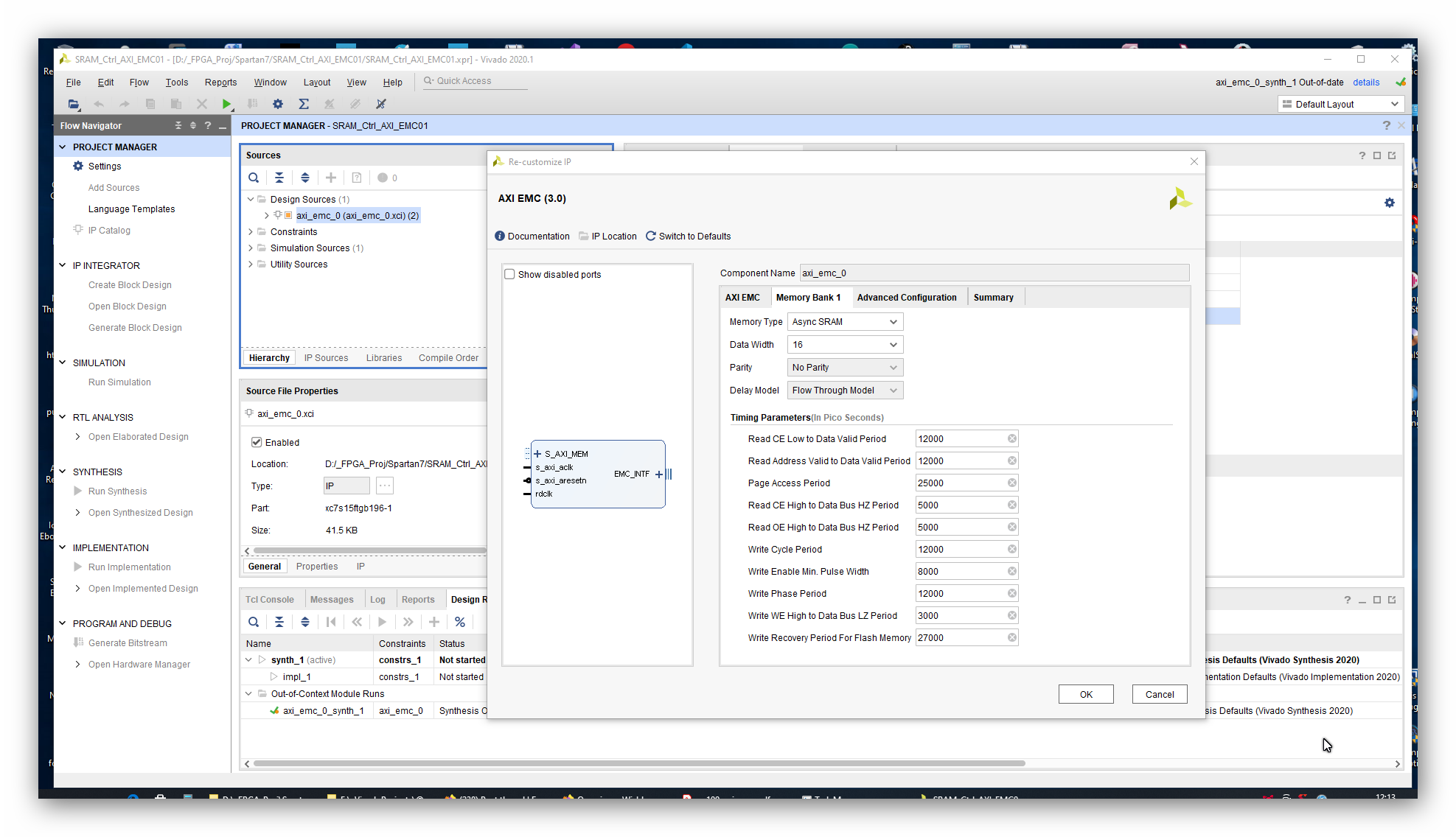

I tried in Vivado project to fulfill all parameters for my memory IC (CY7C1041DV33) - see screenshot:

The problem is that this IPCore interface is very complicated - both AXI part end SRAM IC. Here is generated for this IP Core VHDL entity port:

I am aware that next step should be adding to project Soft-Processor (for example Xilinx Microblaze ) which is able to send data to SRAM memory over AXI BUS. I was looking for such example oprojects but this serch was unsuccessful. Could somebody share with me example project wich is using "AXI EMC" (best with Microblaze). But if someone has example code using "AXI EMC" without soft-processor I am aslo interested in it. Any hints to implementing such SRAM controller are warmly welcome.

Thanks in advance and Regards

some time ago I described my struggling with implementatuion for very simple "SRAM controller" - see this link:

https://www.edaboard.com/threads/issue-with-port-buffering-inout-spartan7-board.395904/

After long time this struggle ended with success - this simple controller was working. The issue is that implementation had very bad performance and wasn't suitable for using in real project (for my needs only). It was the reason that I have started looking for better implementation of SRAM controller. I noticed that in "Xilinx Vivado" is available fre IPCore called "AXI EMC v.3.0" (this is shortcut for: AXI External Memory Controller) - see this link:

https://www.xilinx.com/support/documentation/ip_documentation/axi_emc/v3_0/pg100-axi-emc.pdf

I tried in Vivado project to fulfill all parameters for my memory IC (CY7C1041DV33) - see screenshot:

--- Updated ---

The problem is that this IPCore interface is very complicated - both AXI part end SRAM IC. Here is generated for this IP Core VHDL entity port:

Code:

ENTITY axi_emc_0 IS

PORT (

s_axi_aclk : IN STD_LOGIC;

s_axi_aresetn : IN STD_LOGIC;

rdclk : IN STD_LOGIC;

s_axi_mem_awid : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s_axi_mem_awaddr : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

s_axi_mem_awlen : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

s_axi_mem_awsize : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

s_axi_mem_awburst : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

s_axi_mem_awlock : IN STD_LOGIC;

s_axi_mem_awcache : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s_axi_mem_awprot : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

s_axi_mem_awvalid : IN STD_LOGIC;

s_axi_mem_awready : OUT STD_LOGIC;

s_axi_mem_wdata : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

s_axi_mem_wstrb : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s_axi_mem_wlast : IN STD_LOGIC;

s_axi_mem_wvalid : IN STD_LOGIC;

s_axi_mem_wready : OUT STD_LOGIC;

s_axi_mem_bid : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

s_axi_mem_bresp : OUT STD_LOGIC_VECTOR(1 DOWNTO 0);

s_axi_mem_bvalid : OUT STD_LOGIC;

s_axi_mem_bready : IN STD_LOGIC;

s_axi_mem_arid : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s_axi_mem_araddr : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

s_axi_mem_arlen : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

s_axi_mem_arsize : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

s_axi_mem_arburst : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

s_axi_mem_arlock : IN STD_LOGIC;

s_axi_mem_arcache : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s_axi_mem_arprot : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

s_axi_mem_arvalid : IN STD_LOGIC;

s_axi_mem_arready : OUT STD_LOGIC;

s_axi_mem_rid : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

s_axi_mem_rdata : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

s_axi_mem_rresp : OUT STD_LOGIC_VECTOR(1 DOWNTO 0);

s_axi_mem_rlast : OUT STD_LOGIC;

s_axi_mem_rvalid : OUT STD_LOGIC;

s_axi_mem_rready : IN STD_LOGIC;

mem_dq_i : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

mem_dq_o : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

mem_dq_t : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

mem_a : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

mem_ce : OUT STD_LOGIC_VECTOR(0 DOWNTO 0);

mem_cen : OUT STD_LOGIC_VECTOR(0 DOWNTO 0);

mem_oen : OUT STD_LOGIC_VECTOR(0 DOWNTO 0);

mem_wen : OUT STD_LOGIC;

mem_ben : OUT STD_LOGIC_VECTOR(1 DOWNTO 0);

mem_qwen : OUT STD_LOGIC_VECTOR(1 DOWNTO 0);

mem_rpn : OUT STD_LOGIC;

mem_adv_ldn : OUT STD_LOGIC;

mem_lbon : OUT STD_LOGIC;

mem_cken : OUT STD_LOGIC;

mem_rnw : OUT STD_LOGIC;

mem_cre : OUT STD_LOGIC;

mem_wait : IN STD_LOGIC_VECTOR(0 DOWNTO 0)

);

END axi_emc_0;I am aware that next step should be adding to project Soft-Processor (for example Xilinx Microblaze ) which is able to send data to SRAM memory over AXI BUS. I was looking for such example oprojects but this serch was unsuccessful. Could somebody share with me example project wich is using "AXI EMC" (best with Microblaze). But if someone has example code using "AXI EMC" without soft-processor I am aslo interested in it. Any hints to implementing such SRAM controller are warmly welcome.

Thanks in advance and Regards