nihan_A

Newbie level 5

Hello!

I have a problem with driving P channel mosfet.

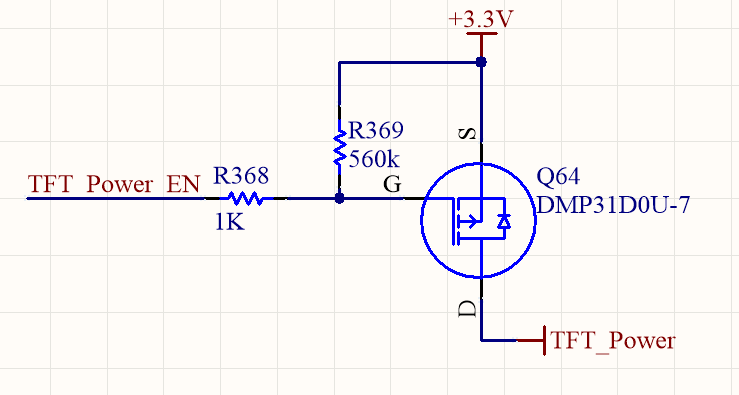

I am trying to control power voltage of a TFT. As you can see below when TFT_Power_EN signal is low I expect there would be 3.3V at the Drain of the mosfet which is labeled as TFT Power. But when I check the signal it is just 2.5V

I understand, since mosfet has its own resistance there would be some loss. But when I check mosfet datasheet 0.8V loss is too much.

I thought maybe TFT wants to draw more current so it result voltage drop so I connect one more mosfet as parallel but no change.

If anyone have experience or any idea please help me.

P.s. Measured current from the drain is 460ma with 2.5V drain voltage

I have a problem with driving P channel mosfet.

I am trying to control power voltage of a TFT. As you can see below when TFT_Power_EN signal is low I expect there would be 3.3V at the Drain of the mosfet which is labeled as TFT Power. But when I check the signal it is just 2.5V

I understand, since mosfet has its own resistance there would be some loss. But when I check mosfet datasheet 0.8V loss is too much.

I thought maybe TFT wants to draw more current so it result voltage drop so I connect one more mosfet as parallel but no change.

If anyone have experience or any idea please help me.

P.s. Measured current from the drain is 460ma with 2.5V drain voltage