George_P

Member level 2

Hi

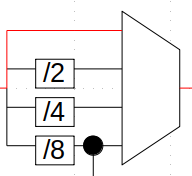

I have the following clk muxing structure: 4 input clocks (let's say clk1, clk2, clk3, clk4), all with the same source (clk1), 3 of them divided.

I tried defining only 1 generated clk for this structure, at the mux output (the non divided, with the max frequency). The master clock (clk1) is also defined and used as source for the generated clk.

The timing report gives timing violations in paths that go through the Select of this multiplexer. These are false paths, so I tried to false-path them. However they are still present, as if false-path is ignored (maybe you cannot false-path "through" the clock tree, but only through the datapath? If anyone knows please share your thoughts).

Any ideas:

1. How should the clock definitions be properly defined for this structure?

2. How to set the tool (e.g Primetime) to ignore paths through the "select" pin?

Thank you

I have the following clk muxing structure: 4 input clocks (let's say clk1, clk2, clk3, clk4), all with the same source (clk1), 3 of them divided.

I tried defining only 1 generated clk for this structure, at the mux output (the non divided, with the max frequency). The master clock (clk1) is also defined and used as source for the generated clk.

The timing report gives timing violations in paths that go through the Select of this multiplexer. These are false paths, so I tried to false-path them. However they are still present, as if false-path is ignored (maybe you cannot false-path "through" the clock tree, but only through the datapath? If anyone knows please share your thoughts).

Any ideas:

1. How should the clock definitions be properly defined for this structure?

2. How to set the tool (e.g Primetime) to ignore paths through the "select" pin?

Thank you