Junus2012

Advanced Member level 5

- Joined

- Jan 9, 2012

- Messages

- 1,552

- Helped

- 47

- Reputation

- 98

- Reaction score

- 53

- Trophy points

- 1,328

- Location

- Italy

- Activity points

- 15,235

Hello,

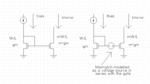

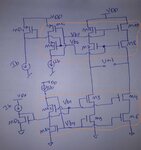

Following my formal post, I am trying to bias the core amplifier by means of biasing current mirror like shown in the image below

As you see, Mx1-Mx4 are the bising mirror to the core amplifier (folded stage),

To save power, I am trying to make Ib less than the needed current in the amplifier then I rise it by means of the mirror ratio, for example I choose mirror ratio of 4,

My question, is it possible to increase the mirror ratio like to make it 10 ? I read somewhere that as more we increase the mirror ratio as more we have less aqurate mirror, is that true ? what is the preferable or reasonable ratio you would suggest

thank you very much

Following my formal post, I am trying to bias the core amplifier by means of biasing current mirror like shown in the image below

As you see, Mx1-Mx4 are the bising mirror to the core amplifier (folded stage),

To save power, I am trying to make Ib less than the needed current in the amplifier then I rise it by means of the mirror ratio, for example I choose mirror ratio of 4,

My question, is it possible to increase the mirror ratio like to make it 10 ? I read somewhere that as more we increase the mirror ratio as more we have less aqurate mirror, is that true ? what is the preferable or reasonable ratio you would suggest

thank you very much