Junus2012

Advanced Member level 5

Dear friends,

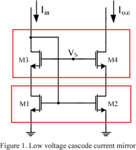

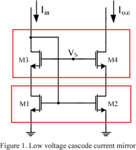

Attached is an image of the simple wide swing current,

in layout I am matching M1 with M2 in one group, then I match the M3 and M4 separately in other group, then I put M3-M4 above the M1-M2

My question is, can I put the matched transistors M3-M4 beside the matched transistors M1-M2 ?

Thank you very much

Attached is an image of the simple wide swing current,

in layout I am matching M1 with M2 in one group, then I match the M3 and M4 separately in other group, then I put M3-M4 above the M1-M2

My question is, can I put the matched transistors M3-M4 beside the matched transistors M1-M2 ?

Thank you very much