Junus2012

Advanced Member level 5

Dear Friends,

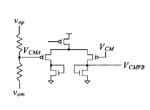

I am converting the attached circuit to fully differential version of it, but it is not working with me, may be the circuit have two mirrors at the output, i am simply converting the up and down mirrors to current source and connecting CMFB to the down one, but the circuit is not functioning,

I would appreciate your help if you could suggest me the procedure for modifying the circuit to fully differential output

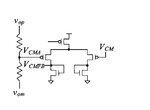

Attached you find please the circuit of the single ended output so you can refer to it in your explanation

Thank you very much in advance

Best Regards

I am converting the attached circuit to fully differential version of it, but it is not working with me, may be the circuit have two mirrors at the output, i am simply converting the up and down mirrors to current source and connecting CMFB to the down one, but the circuit is not functioning,

I would appreciate your help if you could suggest me the procedure for modifying the circuit to fully differential output

Attached you find please the circuit of the single ended output so you can refer to it in your explanation

Thank you very much in advance

Best Regards