eengr

Member level 4

FPGA coding style Behavioural vs structural Modelling

Hi All

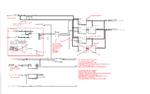

I would like to use Xilinx Spartan-6 XC6SLX9 (TQFP-144) to design an address decoder for ISA Bus. The board would be connected to PC104 and will use ISA bus 8-bit data line to communicate. The task is to:

Off course ISA bus has its IOR & IOW lines that could be read to find out if it is Read operation or Write operation. Also, the clock signal is coming from ISA bus (PC104)

I am new to FPGA design & VHDL. This design has been done in the past by someone using schematic entry on Xilinx ISE using a different Xilinx FPGA device (which has gone obsolete) but I would like to use VHDL for it.

I have seen VHDL generated file of the old design and it looks more like component and instantiation in I think what is known as "Structural Modelling Style" (port mapping is generated for all logical symbols used in schematic entry)

If I look at the task at hand, it looks "simple" to me in that, I think could be implemented by using simple 'if' statements for above 4 cases & many be use CLK signal in process sensitivity list. I understand that it is something called 'Behavioural Modelling Style' i.e., looking at the inputs & outputs only (and treating everything in the middle as black box)

But then I started looking into a book 'Digital System Design with VHDL' by Mark Zwolinski in order to dig bit deeper to find out if 'Behavioural Style' would be a reasonable approach for me to take

I have attached the two pages of his book

with this message

with this message

On page -42 it states that: While this model is perfectly acceptable as a description of a particular logical function, it does not correspond to any normally available piece of circuitry

Now, I am confused and struggling to understand if using Behavioural Modelling style will be good enough for my design OR would I need to start looking into Structural Modelling style? And what are the pros & cons (for this specific case) OR have i got wrong end of stick?

Any help would be greatly appreciated..

Hi All

I would like to use Xilinx Spartan-6 XC6SLX9 (TQFP-144) to design an address decoder for ISA Bus. The board would be connected to PC104 and will use ISA bus 8-bit data line to communicate. The task is to:

- Direct the data from ISA 8-bit data-lines to 1st set of 8-bit OUTPUT lines of FPGA if address on ISA Address bus is say 0x500.

- Direct the data from ISA 8-bit data-lines to 2nd set of 8-bit OUTPUT lines of FPGA if address on ISA Address bus is say 0x502.

- Direct the data from 1st set of 8-bit INPUT lines from FPGA to 8 bit ISA Data bus if the address on ISA Address bus is say 0x503.

- Direct the data from 2nd set of 8-bit INPUT lines from FPGA to 8 bit ISA Data bus if the address on ISA Address bus is say 0x504.

Off course ISA bus has its IOR & IOW lines that could be read to find out if it is Read operation or Write operation. Also, the clock signal is coming from ISA bus (PC104)

I am new to FPGA design & VHDL. This design has been done in the past by someone using schematic entry on Xilinx ISE using a different Xilinx FPGA device (which has gone obsolete) but I would like to use VHDL for it.

I have seen VHDL generated file of the old design and it looks more like component and instantiation in I think what is known as "Structural Modelling Style" (port mapping is generated for all logical symbols used in schematic entry)

If I look at the task at hand, it looks "simple" to me in that, I think could be implemented by using simple 'if' statements for above 4 cases & many be use CLK signal in process sensitivity list. I understand that it is something called 'Behavioural Modelling Style' i.e., looking at the inputs & outputs only (and treating everything in the middle as black box)

But then I started looking into a book 'Digital System Design with VHDL' by Mark Zwolinski in order to dig bit deeper to find out if 'Behavioural Style' would be a reasonable approach for me to take

I have attached the two pages of his book

with this message

with this messageOn page -42 it states that: While this model is perfectly acceptable as a description of a particular logical function, it does not correspond to any normally available piece of circuitry

Now, I am confused and struggling to understand if using Behavioural Modelling style will be good enough for my design OR would I need to start looking into Structural Modelling style? And what are the pros & cons (for this specific case) OR have i got wrong end of stick?

Any help would be greatly appreciated..