khaled2k

Member level 2

Hi all,

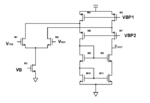

I have a folded cascode opamp with NMOS differential input and the current is steered in PMOS cascode.

The output conductance of all transistors should be theoritically abreviated as

gds= λ Id

I have noticed that for M5 transistor, the simulated gds is much larger than expected.

Let us say for example I5= 50 µA, gds5= 30 µS (Here λ= 0.6V -1)

While for M7, I7= 30 µA, gds7 = 3 µS (Here λ= 0.1V -1)

Even the two transistors are PMOS. Does anyone has an explanation for this?

Thank you guys in advance.

I have a folded cascode opamp with NMOS differential input and the current is steered in PMOS cascode.

The output conductance of all transistors should be theoritically abreviated as

gds= λ Id

I have noticed that for M5 transistor, the simulated gds is much larger than expected.

Let us say for example I5= 50 µA, gds5= 30 µS (Here λ= 0.6V -1)

While for M7, I7= 30 µA, gds7 = 3 µS (Here λ= 0.1V -1)

Even the two transistors are PMOS. Does anyone has an explanation for this?

Thank you guys in advance.