samiran_dam

Full Member level 2

- Joined

- Apr 17, 2010

- Messages

- 122

- Helped

- 3

- Reputation

- 6

- Reaction score

- 3

- Trophy points

- 1,298

- Activity points

- 2,419

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

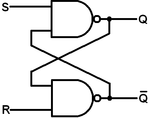

You want the output to be high from the falling edge of 'A' until the falling edge of 'B'. You should be able to use a flip-flop or S-R latch to do that.

Brian.

This is doesn´t answer my questions.o/p will not change its state @posedge of either A or B.

Hi,

do you need real hardware or code (HDL)?

****

Your diagram is not clear.

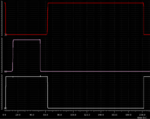

* what happens to the opitput when B is HIGH during the falling edge of A?

* what happens to the opitput when A is LOW during the falling edge of B?

Klaus

Yes, sorry. I meant:* what happens to the opitput when A is LOW during the falling edge of B?

this situation is already shown in the illustration given below.

Please provide an unequivocal function specification. The timing diagram in post #1 is useless because it doesn't show the state before and after the last input signal transition.