immadi.jagadish

Member level 5

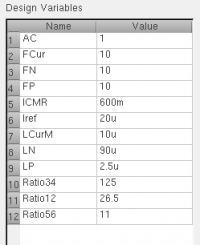

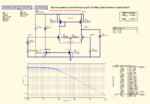

Hi,how to design signle stage OTA with the below specs in cadence 180nm technology.I have referred few book but I couldn't find any relevant info.Please help me with the step by step procedure.

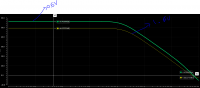

DC gain:min 52dB

Gain BW product: min 6MHz

large signal cutoff frequency :min 6Khz

output common mode:typical value -1.2v

input common mode range CMRi: min 0.6v and max 1.6v

load capacitance :typical 0.5 pf

supply voltage :1.8v

with all transistors minimum area.

DC gain:min 52dB

Gain BW product: min 6MHz

large signal cutoff frequency :min 6Khz

output common mode:typical value -1.2v

input common mode range CMRi: min 0.6v and max 1.6v

load capacitance :typical 0.5 pf

supply voltage :1.8v

with all transistors minimum area.