ammar_kurd

Junior Member level 3

Hello everyone,

In the book "Logic and Computer Design Fundamentals by M.Morris Mano and Charles R.Kime", after defining what a hold-time is and what a propagation-delay is, it is said that "Since Changes of the outputs are separated from the control by the inputs, the minimum propagation-delay time should be longer than the maximum hold-time "

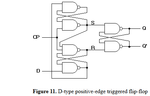

This is related to the edge triggered flip-flop.

I don't get this, how is it so? can someone explain.

Thanks in advance.

In the book "Logic and Computer Design Fundamentals by M.Morris Mano and Charles R.Kime", after defining what a hold-time is and what a propagation-delay is, it is said that "Since Changes of the outputs are separated from the control by the inputs, the minimum propagation-delay time should be longer than the maximum hold-time "

This is related to the edge triggered flip-flop.

I don't get this, how is it so? can someone explain.

Thanks in advance.