Vijay Vinay

Member level 5

Hello,

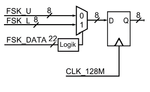

I have a VHDL block that performs FSK modulation. It looks like this

.

.

The operation of the VHDL block goes like this. Fsk_data selects Fsk_u or Fsk_l depending upon its bit value( either 0 or 1). The 'Logik' block decides which bit of fsk_data to be used to set this multiplexer. What I need to do is to implement the counter function for this Logik block that increases with every clock cycle and when reached the maximum value will start again with zero.

The architecture of my VHDL code is as follows:

But, after this I don't have any idea how to proceed. My point is that I need to point the next address of the fsk_data register using the cnt_s (cnt_s acts as a pointer here) in order to select either fsk_u or fsk_l. I need to know whether my point is right. Help is appreciated in proceeding this code.

I have a VHDL block that performs FSK modulation. It looks like this

.

. The operation of the VHDL block goes like this. Fsk_data selects Fsk_u or Fsk_l depending upon its bit value( either 0 or 1). The 'Logik' block decides which bit of fsk_data to be used to set this multiplexer. What I need to do is to implement the counter function for this Logik block that increases with every clock cycle and when reached the maximum value will start again with zero.

The architecture of my VHDL code is as follows:

Code VHDL - [expand]

But, after this I don't have any idea how to proceed. My point is that I need to point the next address of the fsk_data register using the cnt_s (cnt_s acts as a pointer here) in order to select either fsk_u or fsk_l. I need to know whether my point is right. Help is appreciated in proceeding this code.

Last edited by a moderator: