abhishekgrover

Newbie level 5

Hi,

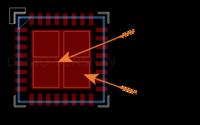

I want to design footprint for QFN48 and QFN16 package.

Please suggest some pdfs or tutorials that I should study to design these footprints in orcad.

Best Regards,

Abhishek Grover.

I want to design footprint for QFN48 and QFN16 package.

Please suggest some pdfs or tutorials that I should study to design these footprints in orcad.

Best Regards,

Abhishek Grover.