zhangljz

Member level 5

- Joined

- Oct 19, 2013

- Messages

- 81

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 8

- Activity points

- 648

Hello,

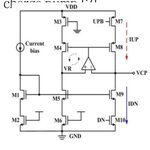

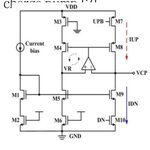

I am designing a PLL, but get stuck at the charge pump. I use the below structure. WHen I do transient simulation, I got oscillation on the output of charge pump. The loop filter parameters are calculated to meet to requirement of "PLL bandwidth < 1/20 reference frequency"

The detailed simulation are as below, what is the problem with this ringing?

And the charge pump has a large peak current at the falling edge of 'upb', how to solve this problem?

The switch is to setup the initial voltage

The simulation:

Thank you in advance

I am designing a PLL, but get stuck at the charge pump. I use the below structure. WHen I do transient simulation, I got oscillation on the output of charge pump. The loop filter parameters are calculated to meet to requirement of "PLL bandwidth < 1/20 reference frequency"

The detailed simulation are as below, what is the problem with this ringing?

And the charge pump has a large peak current at the falling edge of 'upb', how to solve this problem?

The switch is to setup the initial voltage

The simulation:

Thank you in advance