SamV

Newbie level 6

Hi All,

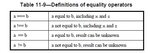

Today I thought I was clever by using a high impedance state in verilog. It doesn't work when I simulate it. Below is effectively what I was trying to do. Based on the simulation it seems that the if statement in the second always block which should check if the register set has a value of 1'bz doesn't work even though the value in the register is 1'bz. Is this what I should expect? If so, is there a way of doing this?

Thanks,

Sam

Today I thought I was clever by using a high impedance state in verilog. It doesn't work when I simulate it. Below is effectively what I was trying to do. Based on the simulation it seems that the if statement in the second always block which should check if the register set has a value of 1'bz doesn't work even though the value in the register is 1'bz. Is this what I should expect? If so, is there a way of doing this?

Thanks,

Sam

Code Verilog - [expand]

Last edited by a moderator: