Jester

Full Member level 6

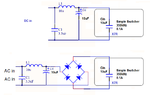

Can anyone recommend a design tool for optimizing a conducted emissions filter?

This is low power for a 50V to 5V LM46000 simple switcher, < 2W

Thanks

This is low power for a 50V to 5V LM46000 simple switcher, < 2W

Thanks