u24c02

Advanced Member level 1

Hi.

I didn't quite catch the following posting's answer from other people.

How could I calculate this questions?

Would you please let me know?

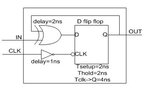

Given the above design,reference the figure

1.What are the effective setup and hold times between IN and CLK in the above circuit?

A. Tsetup = 4 ns, Thold = 1 ns

B. Tsetup = 3 ns, Thold = 0 ns

C. Tsetup = 3 ns, Thold = 1ns

D. Tsetup = 2 ns, Thold = 0 ns

2.What is the maximum operating frequency of the above circuit?

A. 250 MHz

B. 80 MHz

C. 125 MHz

D. 166.7 MHz

I didn't quite catch the following posting's answer from other people.

How could I calculate this questions?

Would you please let me know?

Given the above design,reference the figure

1.What are the effective setup and hold times between IN and CLK in the above circuit?

A. Tsetup = 4 ns, Thold = 1 ns

B. Tsetup = 3 ns, Thold = 0 ns

C. Tsetup = 3 ns, Thold = 1ns

D. Tsetup = 2 ns, Thold = 0 ns

2.What is the maximum operating frequency of the above circuit?

A. 250 MHz

B. 80 MHz

C. 125 MHz

D. 166.7 MHz