je01911

Junior Member level 1

Hi guys

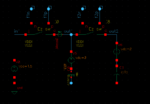

I am trying to simulate the PSS & Pnoise of simple sample and for circuit for thermal noise simulation.

The clock signal for gate voltage swings from 0 to 2.4V (for rail to rail sampling)

The input source (PORT0) generates sine signal from 0 to 1.2V

Accoring to kT/C noise theory, I expect to noise power as much as 37.692nV²/Hz because of 100fF load capacitance.

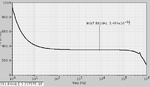

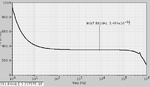

However, the simulation results shows just 0.3464fV²/Hz at flat zone (white noise by thermal) like

I can't understand why the value computed by theory is different with simulation results in aspect of thermal noise.

If you knows the reason, please help me.

I am trying to simulate the PSS & Pnoise of simple sample and for circuit for thermal noise simulation.

The clock signal for gate voltage swings from 0 to 2.4V (for rail to rail sampling)

The input source (PORT0) generates sine signal from 0 to 1.2V

Accoring to kT/C noise theory, I expect to noise power as much as 37.692nV²/Hz because of 100fF load capacitance.

However, the simulation results shows just 0.3464fV²/Hz at flat zone (white noise by thermal) like

I can't understand why the value computed by theory is different with simulation results in aspect of thermal noise.

If you knows the reason, please help me.