william_luo

Junior Member level 2

Hi, all

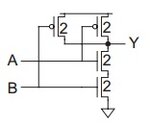

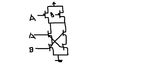

I have a question about transistors matching. For inverter, I know that the width ratio of pmos to nmos is nearly 2:1 (tsmc18) for getting equal rising and falling time. I just wonder, for other circuits, like NAND2 or XOR2, do I need to match transistors for worst case? (like NAND2 shown below, in this case, )

When I took this course in class, the lab tutorial just told me that for two input cases (NAND2 or XOR2), give one input VDD, change other input signal. But obviously, this is not the worst case. Can someone explain this for me? Thank you in advance.

Regards,

I have a question about transistors matching. For inverter, I know that the width ratio of pmos to nmos is nearly 2:1 (tsmc18) for getting equal rising and falling time. I just wonder, for other circuits, like NAND2 or XOR2, do I need to match transistors for worst case? (like NAND2 shown below, in this case, )

When I took this course in class, the lab tutorial just told me that for two input cases (NAND2 or XOR2), give one input VDD, change other input signal. But obviously, this is not the worst case. Can someone explain this for me? Thank you in advance.

Regards,

Attachments

Last edited: