skoda

Junior Member level 3

Hi to all great designers !

In allen Holberg I find this page and I see that mathing of two transistor is a point of problem (ie. current density should be equal and I do matching NMOS to NMOS)

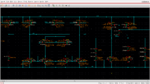

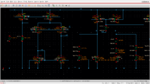

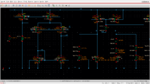

I`m trying to make Bandgap ref 1V supply, now I have problem with systematic offset, which I see between Vgs(N_CLl) and VDS( N_CLr). This two voltage should be equal right?

But in my circuit the second stage is PMOS( P_BGRl) and there is a problem with mathing right? Because I can do same current density but this two device has different threshold voltage. So I try to make current density equal but Im not sure if this is good solution.

In allen Holberg I find this page and I see that mathing of two transistor is a point of problem (ie. current density should be equal and I do matching NMOS to NMOS)

I`m trying to make Bandgap ref 1V supply, now I have problem with systematic offset, which I see between Vgs(N_CLl) and VDS( N_CLr). This two voltage should be equal right?

But in my circuit the second stage is PMOS( P_BGRl) and there is a problem with mathing right? Because I can do same current density but this two device has different threshold voltage. So I try to make current density equal but Im not sure if this is good solution.