Kick

Full Member level 6

- Joined

- Sep 27, 2010

- Messages

- 345

- Helped

- 16

- Reputation

- 32

- Reaction score

- 15

- Trophy points

- 1,298

- Location

- India,Bangalore

- Activity points

- 3,178

hiii all,

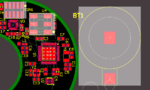

I have a problem in Altium PCB doc. In my project some footprints designed by me only. Problem is a transparent keep-out area is visible (while clicking above that footprint) around that footprints,because of that I can't place components near to that footprint,but I can route in that area. How can I solve this problem?? Can I edit that area?

I have a problem in Altium PCB doc. In my project some footprints designed by me only. Problem is a transparent keep-out area is visible (while clicking above that footprint) around that footprints,because of that I can't place components near to that footprint,but I can route in that area. How can I solve this problem?? Can I edit that area?