electronicman26

Full Member level 2

hi

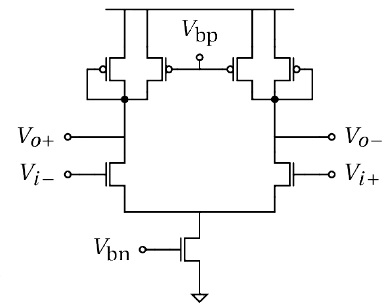

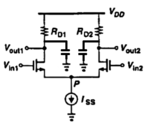

I want to calculate delay time for this cell with analytic equation and software, but I don't know how I do this

I would be glad if anyone help me to do this

I want to calculate delay time for this cell with analytic equation and software, but I don't know how I do this

I would be glad if anyone help me to do this