subbu2

Newbie level 6

- Joined

- Apr 3, 2014

- Messages

- 12

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 101

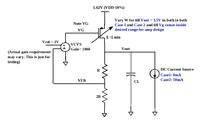

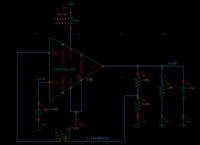

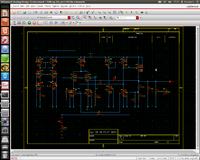

I am designing an LDO with following specs..

Vin : 1.8V +/- 10%

Vout : 1.5V +/- 3%

Vref : 1V +/- 1%

Iload : 0 to 50mA

Ext Cap : 100nF +/- 20%

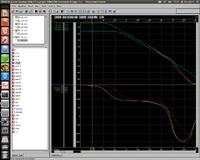

PSR : >40dB upto 10MHz

please suggest me the way forward (where to begin the design wat parameters and architectures to look at etc.)..I have read abt the Single stage diff amp and abt miller compensation after adding second stage and yet to start wit the design.

Vin : 1.8V +/- 10%

Vout : 1.5V +/- 3%

Vref : 1V +/- 1%

Iload : 0 to 50mA

Ext Cap : 100nF +/- 20%

PSR : >40dB upto 10MHz

please suggest me the way forward (where to begin the design wat parameters and architectures to look at etc.)..I have read abt the Single stage diff amp and abt miller compensation after adding second stage and yet to start wit the design.

Last edited: