samabraham

Newbie level 6

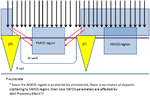

I have seen in PDKs spacing for NMOS from Nwell. Can anyone explain how an NMOS will get affected during Nwell fabrication??:!:

please help...

please help...

Last edited: